Find the Best Cosmetic Hospitals — Choose with Confidence

Discover top cosmetic hospitals in one place and take the next step toward the look you’ve been dreaming of.

“Your confidence is your power — invest in yourself, and let your best self shine.”

Compare • Shortlist • Decide smarter — works great on mobile too.

Introduction

IC Design & Verification Tools are specialized software platforms used to design, simulate, validate, and optimize integrated circuits (ICs). These tools support the full semiconductor lifecycle—from RTL design and synthesis to physical layout, verification, and final sign-off before fabrication.

As chips become increasingly complex, with billions of transistors and strict performance, power, and area constraints, these tools are essential for ensuring correctness and manufacturability. Verification, in particular, plays a critical role in preventing costly errors before fabrication.

Common use cases include:

- ASIC and SoC design (digital, analog, mixed-signal)

- RTL design using Verilog and VHDL

- Functional and formal verification

- Physical design (placement, routing, timing closure)

- Power, thermal, and signal integrity analysis

What buyers should evaluate:

- RTL design and synthesis capabilities

- Simulation and verification depth (UVM, formal methods)

- Scalability for large designs

- Integration across the full design flow

- Performance and runtime efficiency

- Automation and scripting support

- Ecosystem (IP libraries, PDK compatibility)

- Deployment flexibility (cloud or on-premise)

- Debugging and visualization tools

- Security and collaboration features

Best for: Semiconductor companies, chip designers, VLSI engineers, FPGA developers, and research labs.

Not ideal for: Beginners or teams working only on basic electronics or PCB-level designs.

Key Trends in IC Design & Verification Tools

- AI-assisted design optimization improving timing, power, and layout efficiency

- Automation of verification workflows reducing manual testing effort

- Shift-left verification enabling earlier bug detection in design cycles

- Cloud-based EDA environments supporting distributed engineering teams

- Rise of chiplet and heterogeneous architectures requiring new workflows

- Integration of system-level simulation and digital twins

- Hardware-assisted verification (emulation and FPGA prototyping)

- Open-source EDA adoption in academia and startups

- Subscription and usage-based pricing models

- Enhanced security for intellectual property protection

How We Selected These Tools (Methodology)

- Evaluated industry adoption and market leadership

- Assessed coverage across the IC design lifecycle

- Reviewed performance in large-scale ASIC and SoC designs

- Considered verification depth and automation features

- Analyzed integration with IP libraries and PDK ecosystems

- Included a mix of enterprise-grade and open-source tools

- Evaluated ease of use and learning curve

- Considered deployment flexibility and scalability

- Prioritized tools with proven reliability in production environments

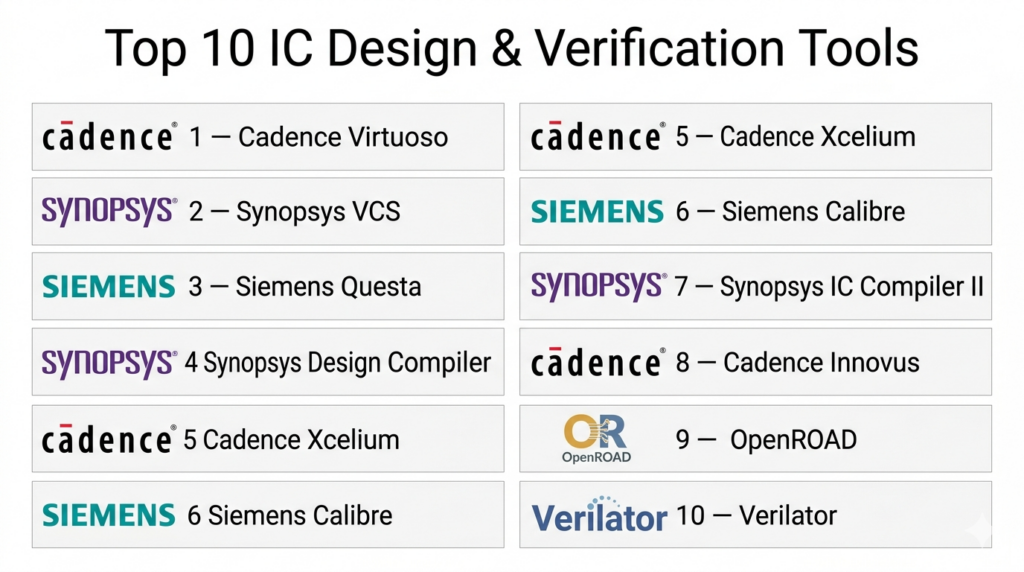

Top 10 IC Design & Verification Tools

#1 — Cadence Virtuoso

Short description (2–3 lines): A leading platform for analog and mixed-signal IC design, widely used for custom chip development.

Key Features

- Custom IC schematic and layout design

- Analog and RF simulation

- Parasitic extraction

- Constraint-driven design

- Integrated verification tools

- Advanced node support

Pros

- Industry-standard for analog design

- Highly accurate simulation

Cons

- Expensive

- Steep learning curve

Platforms / Deployment

Linux; Self-hosted

Security & Compliance

Not publicly stated

Integrations & Ecosystem

Deep integration within Cadence ecosystem.

- PDK compatibility

- APIs and scripting

- Verification tools

Support & Community

Strong enterprise support and widespread adoption.

#2 — Synopsys VCS

Short description (2–3 lines): A high-performance simulation tool for digital verification using SystemVerilog and UVM.

Key Features

- RTL simulation

- UVM support

- Functional coverage

- Debugging tools

- Scalable architecture

- Integration with synthesis tools

Pros

- Fast simulation speeds

- Robust verification capabilities

Cons

- Complex configuration

- High licensing cost

Platforms / Deployment

Linux; Self-hosted

Security & Compliance

Not publicly stated

Integrations & Ecosystem

Part of Synopsys ecosystem.

- Design Compiler

- Verification tools

- APIs

Support & Community

Enterprise-grade support and documentation.

#3 — Siemens Questa

Short description (2–3 lines): A comprehensive verification platform supporting digital, analog, and mixed-signal designs.

Key Features

- Functional and formal verification

- SystemVerilog and UVM support

- Mixed-signal simulation

- Debugging tools

- Coverage analysis

- AI-assisted verification

Pros

- Strong verification capabilities

- Scalable for complex SoC designs

Cons

- Requires expertise

- Expensive

Platforms / Deployment

Windows / Linux; Self-hosted

Security & Compliance

Not publicly stated

Integrations & Ecosystem

Part of Siemens EDA suite.

- Simulation tools

- Verification frameworks

- APIs

Support & Community

Strong enterprise support.

#4 — Synopsys Design Compiler

Short description (2–3 lines): Industry-leading synthesis tool for converting RTL into optimized gate-level designs.

Key Features

- RTL synthesis

- Timing optimization

- Power optimization

- Constraint-driven design

- High scalability

- Integration with verification tools

Pros

- Best-in-class synthesis

- High optimization accuracy

Cons

- Complex workflows

- Expensive

Platforms / Deployment

Linux; Self-hosted

Security & Compliance

Not publicly stated

Integrations & Ecosystem

Strong integration within Synopsys flow.

- Verification tools

- Timing analysis

- APIs

Support & Community

Enterprise support available.

#5 — Cadence Xcelium

Short description (2–3 lines): A scalable simulation platform for digital and mixed-signal verification.

Key Features

- High-speed simulation

- Mixed-signal support

- Debugging tools

- Functional coverage

- UVM compatibility

- Scalable architecture

Pros

- Fast and efficient

- Strong debugging capabilities

Cons

- Licensing cost

- Complex setup

Platforms / Deployment

Linux; Self-hosted

Security & Compliance

Not publicly stated

Integrations & Ecosystem

Part of Cadence ecosystem.

- Virtuoso

- Simulation tools

- APIs

Support & Community

Enterprise-level support.

#6 — Siemens Calibre

Short description (2–3 lines): A leading tool for physical verification and sign-off in IC design.

Key Features

- DRC and LVS verification

- Parasitic extraction

- Reliability analysis

- Design-for-manufacturing checks

- 3D IC verification

- Sign-off validation

Pros

- Industry-standard for sign-off

- High accuracy

Cons

- Resource-intensive

- Complex workflows

Platforms / Deployment

Linux; Self-hosted

Security & Compliance

Not publicly stated

Integrations & Ecosystem

Integrates with major design tools.

- Layout tools

- Verification systems

- APIs

Support & Community

Widely adopted with strong support.

#7 — Synopsys IC Compiler II

Short description (2–3 lines): A physical design tool for placement, routing, and optimization of IC layouts.

Key Features

- Placement and routing

- Timing closure

- Power optimization

- Design rule checks

- Automation features

- Advanced node support

Pros

- Strong backend capabilities

- Scalable for large designs

Cons

- Complex learning curve

- Expensive

Platforms / Deployment

Linux; Self-hosted

Security & Compliance

Not publicly stated

Integrations & Ecosystem

Part of Synopsys ecosystem.

- Design Compiler

- Verification tools

- APIs

Support & Community

Enterprise-grade support.

#8 — Cadence Innovus

Short description (2–3 lines): A digital implementation platform for advanced IC physical design workflows.

Key Features

- Placement and routing

- Timing optimization

- Power analysis

- Floorplanning

- Automation tools

- Scalable architecture

Pros

- Strong performance

- Integrated workflow

Cons

- High cost

- Requires expertise

Platforms / Deployment

Linux; Self-hosted

Security & Compliance

Not publicly stated

Integrations & Ecosystem

Integrated with Cadence ecosystem.

- Virtuoso

- Verification tools

- APIs

Support & Community

Strong enterprise support.

#9 — OpenROAD

Short description (2–3 lines): An open-source framework for automated RTL-to-GDSII physical design flow.

Key Features

- Automated design flow

- Placement and routing

- Timing analysis

- Open-source flexibility

- Script-based workflows

- Integration with open PDKs

Pros

- Free and accessible

- Growing ecosystem

Cons

- Less mature

- Requires technical expertise

Platforms / Deployment

Linux; Self-hosted

Security & Compliance

Not publicly stated

Integrations & Ecosystem

Open-source ecosystem.

- APIs

- Community tools

- Extensions

Support & Community

Active academic and developer community.

#10 — Verilator

Short description (2–3 lines): A fast, open-source Verilog simulator for digital verification workflows.

Key Features

- Verilog simulation

- High performance

- C++ model generation

- Debugging tools

- Integration with toolchains

- Open-source extensibility

Pros

- Very fast execution

- Free and flexible

Cons

- Limited GUI

- Requires programming knowledge

Platforms / Deployment

Windows / macOS / Linux; Self-hosted

Security & Compliance

Not publicly stated

Integrations & Ecosystem

Flexible integration capabilities.

- Toolchains

- Simulation frameworks

- APIs

Support & Community

Strong open-source community.

Comparison Table (Top 10)

| Tool Name | Best For | Platform(s) Supported | Deployment | Standout Feature | Public Rating |

|---|---|---|---|---|---|

| Cadence Virtuoso | Analog IC design | Linux | Self-hosted | Custom IC workflow | N/A |

| Synopsys VCS | RTL verification | Linux | Self-hosted | High-speed simulation | N/A |

| Siemens Questa | Verification | Win/Linux | Self-hosted | Mixed-signal support | N/A |

| Design Compiler | Synthesis | Linux | Self-hosted | RTL optimization | N/A |

| Xcelium | Simulation | Linux | Self-hosted | Scalable verification | N/A |

| Calibre | Sign-off | Linux | Self-hosted | DRC/LVS accuracy | N/A |

| IC Compiler II | Physical design | Linux | Self-hosted | Placement & routing | N/A |

| Innovus | Backend design | Linux | Self-hosted | Timing optimization | N/A |

| OpenROAD | Open-source flow | Linux | Self-hosted | RTL-to-GDS automation | N/A |

| Verilator | Simulation | Win/macOS/Linux | Self-hosted | Fast Verilog simulation | N/A |

Evaluation & Scoring of IC Design & Verification Tools

| Tool Name | Core (25%) | Ease (15%) | Integrations (15%) | Security (10%) | Performance (10%) | Support (10%) | Value (15%) | Weighted Total |

|---|---|---|---|---|---|---|---|---|

| Cadence Virtuoso | 10 | 5 | 9 | 7 | 10 | 9 | 5 | 8.1 |

| Synopsys VCS | 9 | 6 | 9 | 7 | 10 | 9 | 6 | 8.4 |

| Siemens Questa | 9 | 6 | 9 | 7 | 9 | 9 | 6 | 8.2 |

| Design Compiler | 10 | 5 | 9 | 7 | 10 | 9 | 5 | 8.1 |

| Xcelium | 9 | 6 | 8 | 6 | 9 | 8 | 6 | 7.9 |

| Calibre | 10 | 5 | 9 | 7 | 10 | 9 | 5 | 8.1 |

| IC Compiler II | 9 | 5 | 8 | 6 | 9 | 8 | 5 | 7.7 |

| Innovus | 9 | 6 | 8 | 6 | 9 | 8 | 5 | 7.8 |

| OpenROAD | 7 | 6 | 7 | 5 | 7 | 7 | 10 | 7.4 |

| Verilator | 7 | 7 | 7 | 5 | 8 | 7 | 10 | 7.6 |

How to interpret scores:

- Scores are comparative across tools, not absolute

- Higher scores indicate stronger overall balance

- Enterprise tools dominate in performance and scalability

- Open-source tools provide strong value but require expertise

- Use this table to shortlist tools based on priorities

Which IC Design & Verification Tools Tool Is Right for You?

Solo / Freelancer

- Best: OpenROAD, Verilator

- Suitable for learning and small-scale projects

SMB

- Best: Xcelium, Siemens Questa

- Balanced verification and usability

Mid-Market

- Best: Synopsys VCS, Design Compiler

- Strong synthesis and verification workflows

Enterprise

- Best: Cadence Virtuoso, Synopsys, Siemens Calibre

- Full-chip design and sign-off capabilities

Budget vs Premium

- Budget: OpenROAD, Verilator

- Premium: Cadence, Synopsys

Feature Depth vs Ease of Use

- Deep: Cadence, Synopsys

- Easier: Open-source tools

Integrations & Scalability

- Strong ecosystems: Cadence, Synopsys, Siemens

- Flexible: Open-source tools

Security & Compliance Needs

- Enterprise: Commercial EDA tools

- Basic: Open-source solutions

Frequently Asked Questions (FAQs)

What are IC design tools used for?

They are used to design, simulate, and verify integrated circuits before manufacturing.

Why is verification important?

It ensures the chip works correctly and prevents costly fabrication errors.

Are these tools expensive?

Enterprise tools are expensive; open-source tools are free.

What languages are used?

Verilog, VHDL, and SystemVerilog are commonly used.

Can beginners use these tools?

Yes, but they require significant learning.

What is RTL design?

It describes digital circuit behavior using hardware description languages.

What is physical design?

It involves placement and routing of circuit components.

Do these tools support cloud?

Some tools support cloud-based workflows.

Can I switch tools?

Yes, but it requires retraining and workflow changes.

What industries use IC tools?

Semiconductor, automotive, telecom, and AI industries.

Conclusion

IC Design & Verification Tools are essential for modern semiconductor development, enabling engineers to design complex chips with accuracy and efficiency. From enterprise-grade platforms to open-source frameworks, each tool serves a specific role depending on your needs.